실습 예시

1) 실습 도구

Euresys CXP2.0 B’D (PC3603)

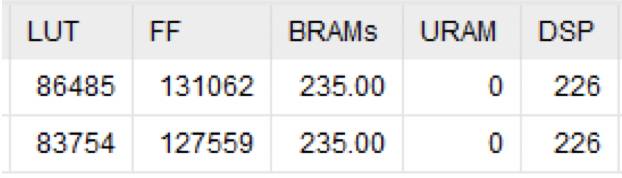

FPGA Chip

Xilinx Kintex Ultrascale XCKU035

(91% DSP, 82% FF, 74% LUT and 56% BRAM resources)

(2GB capacity, 12GB/s bandwidth, shared on-board DRAM memory)

2) 구현 기능

Pixel Threshold

3) 메인 파일 정보

CustomLogicPkt.vhdp (VHDL 사용)

Size: 2,761 KB

기본 실습 보드와는 차원이 다른 개수다. (실습 보드는 10개 내외)

카메라 FPGA 칩과 비교해도 고해상도 & CXP 조합에서 볼 수 있는 정도의 개수다.

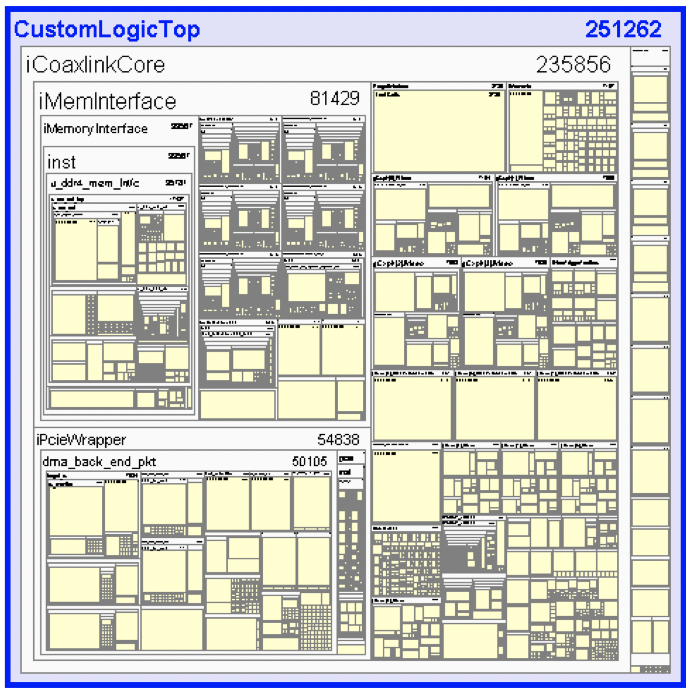

4) Source

- CustomLogicTop: FPGA 설계 코드 (이 안에 iCoaxlinkCore와 iCustomLogic 코드가 있음)

- tb_top: FPGA simulation 코드

- CustomLogic.xdc: FPGA의 HW 핀과 Timing 정보 담긴 코드

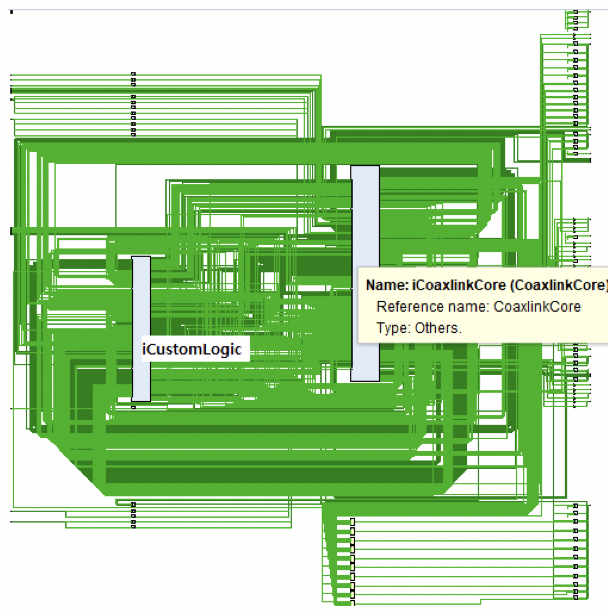

5) Schematic

Schematic 역시 복잡하게 이루어져 있다.

간단하게는 iCustomLogic과 iCoaxlinkCore register로 이루어져 있다.

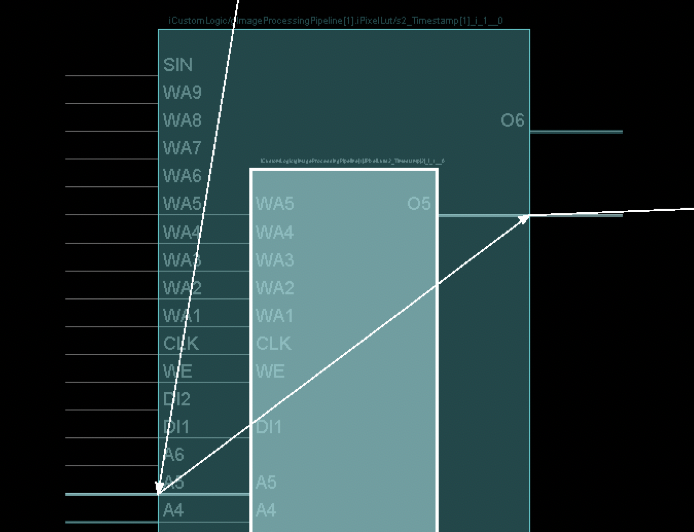

6) Device

Xilinx Kintex 칩의 HW 핀 맵이며

적용 코드를 따라 PixelLUT 핀에 연결되어 있다.

Schematic과 HW 핀 맵 매칭

7) Hierarachy

8) Bitstream 결과 – Power

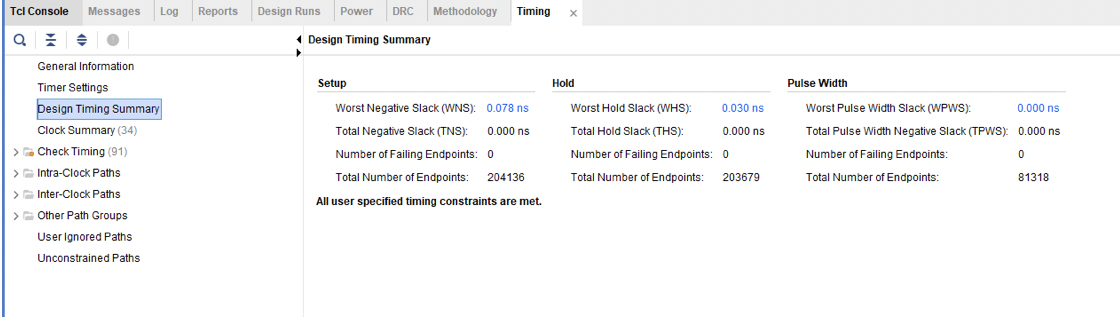

9) Bitstream 결과 – Timing

주의점

- 기능 수정은 .cpp 파일에서 가능하다 (C++ 사용)

- 기능을 수정하면 새로운 bitstream을 추출하기 위해 재합성을 해야 되는데 FPGA가 무겁다 보니 적어도 2시간은 걸린다.

'Digital Logic > FPGA' 카테고리의 다른 글

| [FPGA/Digital 회로 설계] 'WaveDrom'으로 Timing diagram 쉽게 그리기 (0) | 2021.05.31 |

|---|---|

| [IP 설계] AXI4-Lite Interface 란? (0) | 2021.05.11 |

| FPGA 설계에 있어 중요한 점은? 큰 줄기를 잡고 가자 (0) | 2021.05.05 |

| Vivado 프로그램 이란? (0) | 2021.04.11 |

| FPGA 란? (구조, 요소들의 기능) (0) | 2021.04.11 |

댓글