조합 논리 회로(Combinational logic circuits)

출력이 단지 현재의 입력 값에 의해서만 결정된다.

이 말의 내포는 과거의 입력 값에도 결정되는 회로가 따로 있다는 것을 알 수 있다. 이 부분은 다음 포스팅에서 다루도록 하겠다.

어찌보면 단순.조합. 논리 회로이다.

"No clock"

종류는 크게 5가지로 나누었다.

Adder, Comparator, Decoder, Encoder, MUX&DEMUX

그럼 순서대로 하나씩 알아보도록 하자.

1. 가산기 (Adder)

- 목적: 입력 인자를 더해서 출력한다.

- 주의점: 덧셈 결과 M bit 안에 표현하지 못하면 'Overflow bit'가 발생한다. 그래서 이를 방지하기 위한 설계를 고려해야 한다. 그걸 Full Adder라고 하며 Carry-in이라는 올림수 파라미터를 사용한다.

- 블록도

- 소스 코드

module full_adder(a, b, c_in, sum, c_out);

input a, b, c_in;

output sum, c_out;

wire [2:0] d_in;

reg [1:0] d_out;

assign d_in = {a, b, c_in};

assign c_out = d_out[1];

assign sum = d_out[0];

always @(d_in)

case (d_in)

3b'000 : d_out = 2'b00;

3b'001 : d_out = 2'b01;

3b'010 : d_out = 2'b01;

3b'011 : d_out = 2'b10;

3b'100 : d_out = 2'b01;

3b'101 : d_out = 2'b10;

3b'110 : d_out = 2'b10;

default : d_out = 2'b11;

endcase

endmodule

2. 비교기 (Comparator)

- 목적: 두 입력을 비교하여 같으면 '1'을 출력, 다르면 '0'을 출력한다.

- 특이점: M bits 비교기는 입력 A, B의 값 동일 비교 뿐만 아니라 어느 값이 더 큰 지에 따라 출력 값을 달리한다.

비교적 쉬운 회로여서 블록도와 소스코드는 생략한다.

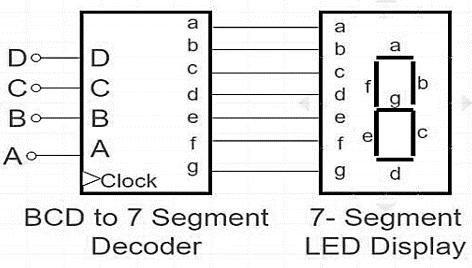

3. Decoder

- 목적: N bits의 정보를 입력해서 2^N 개의 정보를 출력한다. 새롭게 조합해서 출력 값을 만든다.

- 특이점: Enable 핀을 사용하기도 한다.

- 예시: BCD to 7-segment Decoder

- 블록도

- 소스 코드

module bcd2_7segment(bcd, s7segment);

input [3:0] bcd;

output [7:0] s7segment;

reg [7:0] s7segment;

always @(bcd)

if (bcd == 4'b0000)

s7segment = 8'b0011_1111;

else if (bcd == 4'b0001)

s7segment = 8'b0000_0110;

else if (bcd == 4'b0010)

s7segment = 8'b0101_1011;

else if (bcd == 4'b0011)

s7segment = 8'b0100_1111;

else if (bcd == 4'b0100)

s7segment = 8'b0110_0110;

else if (bcd == 4'b0101)

s7segment = 8'b0110_1101;

else if (bcd == 4'b0110)

s7segment = 8'b0111_1101;

else if (bcd == 4'b0111)

s7segment = 8'b0000_0111;

else if (bcd == 4'b1000)

s7segment = 8'b0111_1111;

else if (bcd == 4'b1001)

s7segment = 8'b0110_0111;

else

s7segment = 8'b0000_0000;

endmodule

4. Encoder

- 목적: 2^N 개의 정보를 입력하여 N bits의 정보를 출력한다. 새롭게 조합해서 출력 값을 만든다.

- 예시: Priority encoder (2개 이상의 입력이 동시에 인가될 경우, 입력의 최상위 값에 해당되는 값을 출력)

자세한 사항은 인터넷을 찾길 바란다..ㅎㅎ

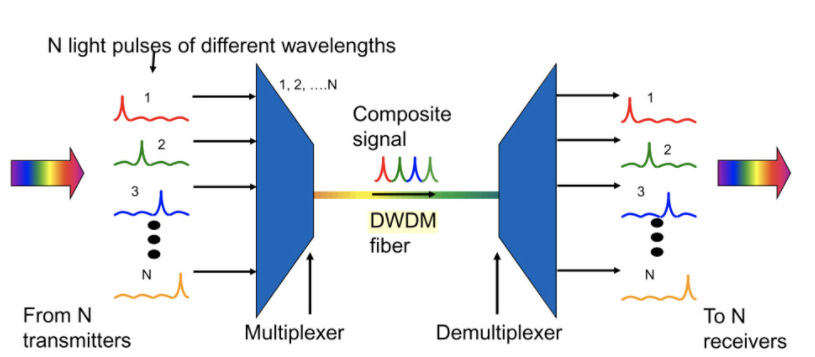

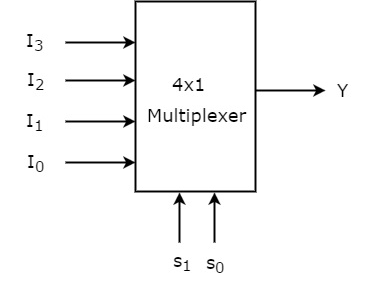

5. MUX & DEMUX (Mutiplexer의 약자)

- 목적: Mux는 여러 개 입력 중 하나를 선택하여 출력으로 내보내고 Demux는 반대로 하나의 입력을 여러 개 출력으로 내보낸다.

- 특이점: Select 핀을 사용하기도 한다.

- 예시: FDM, TDM, DWDM 등..(통신 채널의 대역폭을 효율적으로 할당할 때 사용)

- DWDM 블록도

- 4:1 MUX 블록도

- 소스 코드

module mux_1(i0, i1, i2, i3, sel, y);

input i0, i1, i2, i3;

input [1:0] sel;

output y;

reg y;

always @(sel, i0, i1, i2, i3)

case (sel)

0 : y = i0;

1 : y = i1;

2 : y = i2;

default : y = i3;

endcase

endmodule

'Digital Logic > Verilog' 카테고리의 다른 글

| Verilog 설계에서 중요한 존재들 - Counter (카운터) (0) | 2021.05.10 |

|---|---|

| Verilog 설계에서 중요한 존재들 - 순차 논리 회로(Sequential logic circuits)_#Flip-Flop (0) | 2021.05.09 |

| [기초 개념] Verilog 문법 한눈에 보기 (1) | 2021.04.12 |

| [기초 개념] Verilog 파라미터, 상수 총 정리 (0) | 2021.04.11 |

| [기초 개념] Verilog, SystemVerilog 란? (2) | 2021.04.11 |

댓글